Description

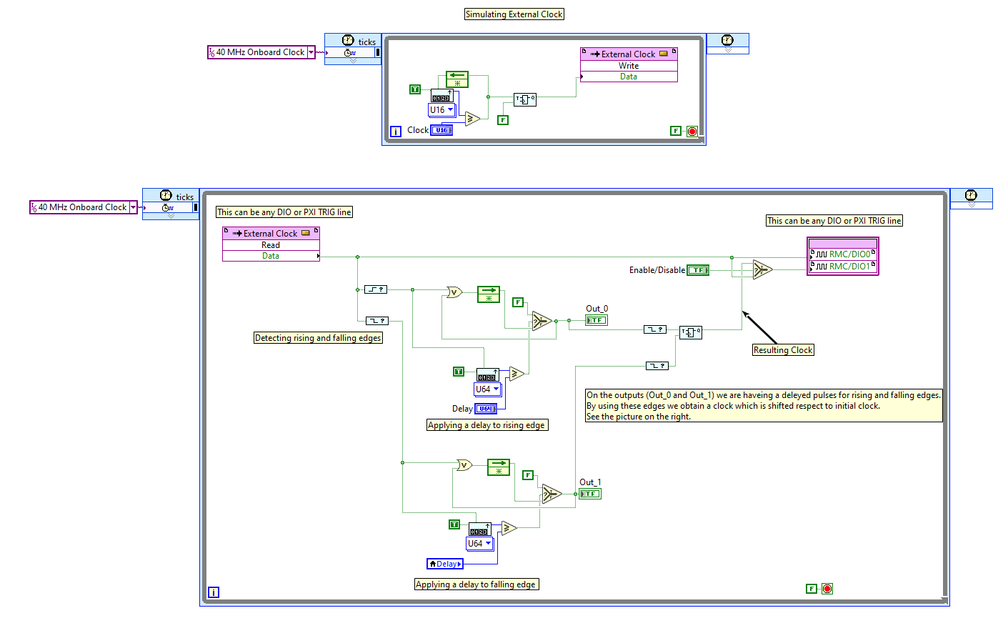

Description-Separate-1This example code demonstrates a controllable delay functionality with LabVIEW FPGA. The example is implemented for sbRIO but can be used for any NI FPGA device.

It allows the user to add a controllable clock delay given to the DIO and returns a clock signal with the specified delay respectfully to the input.

There is a simulated clock in the example, but you can use any DIO or PXI TRIG line as a clock source and any other DIO or PXI TRIG line to output the delayed signal.

See the Block Diagram's content below:

Description-Separate-2