Hi All,

I am sending image data from RT target to FPGA for processing and reading processed image back using FPGA FIFOs.

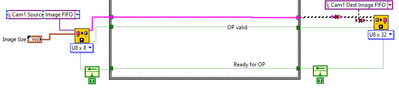

In FPGA code, I am reading FIFO using IMAQ FPGA FIFO to Pixel bus and sending processed image back using IMAQ FPGA Pixel Bus to FIFO function.

It is observed that, Image reception takes more time than transmission to FPGA. I am trying to reduce this time.

On FPGA:

I tried reading U8 image at a rate 8 pixel/read (Max pixel rate for U8 is 😎 and sending back U8 image ata rate 32 pixel/read. I am getting an error as data buses are not same.

Fig: FPGA code

Is there is any way i can transmit U8X8 image and read using higher rate e.g. U8X32, so that it will read more pixels in less time time.

Thanks in advance,

Ashwini A Pandit

Thanks and Regards,

Ashwini A Pandit

Wired-in Software Pty Ltd