- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Slow read rate of a DMA FIFO on my RealTime Host

12-14-2011 10:32 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Everyone,

I've found that I'm unable to read from a "target to host" DMA FIFO at the rate I need. I suspect there are ways to speed this up, so if anyone has any tips I'd appreciate it.

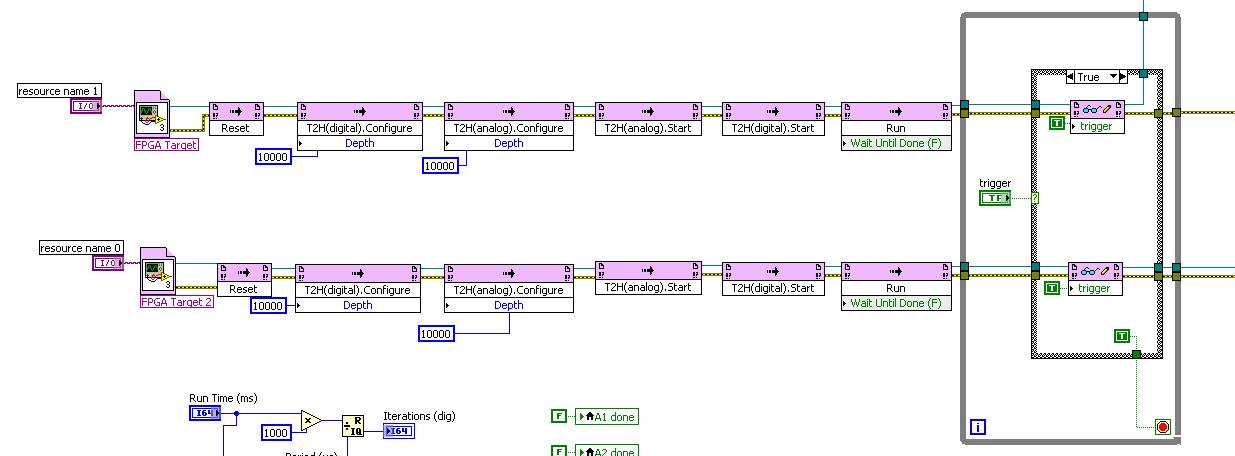

I'm attempting to read 96 digital inputs from an FPGA target (PXI 7825-R) using DMA transfer to a Real Time host (PXIe-8133). On the FPGA target I am writing the 96 bits as 3 U32's, which are written consecutively inside an SCTL running at 5MHz. 3 elements * 5MHz = 15 M elements / sec. Everything seems to be going well on the FPGA side of things.

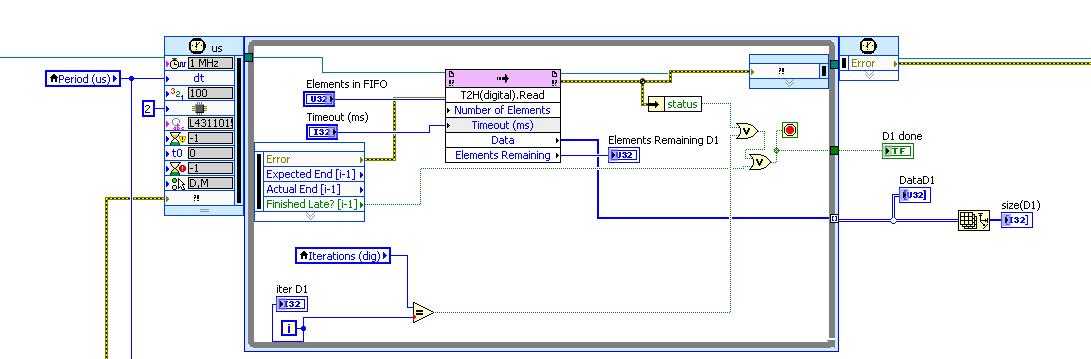

On the RT host, I am reading 10,000 elements in each iteration of a timed loop. Thus I need this loop to run at a rate greater than 1.5KHz in order to keep up with the rate the FPGA is writing at. (10000 elements * 1.5KHz = 15 M elements / s)

Unfortunately, my timed loop on the RT host times out if I set it to run at faster than 0.5 KHz. Testing has shown that the limiting factor is the rate at which the FIFO.read can read the 10,000 elements. I've tried running with fewer elements per read and a higher loop rate, but no combination made a significant difference in the overall rate of elements / sec. I realize that I have some variables and indicators in the loop that could be removed to make it run faster, but I found that stripping the loop down to the bare bones of just the FIFO.read and the stop criteria still didn't achieve a much faster loop rate.

I've added images of the relevant components of my VI's below. Any help is much appreciated. Also, if anyone notices anything else wrong with what I'm doing, please let me know as well.

Thanks alot!

JP

FIFO read loop on RT host

Configuration and start up of FPGA and FIFO on the RT

DMA write loop on the FPGA

12-21-2011 11:01 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

One of your biggest problems could be stemming from having the sequence structure inside the single cycle timed loop. You are writing to the same fifo 3 times inside one cycle. A better approach would be to pack your three elements into a cluster and then write one cluster to the fifo. You can also try to use 3 different target to host fifos as well.