- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- « Previous

- Next »

Error -61496 during FPGA compile

04-17-2015 02:48 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

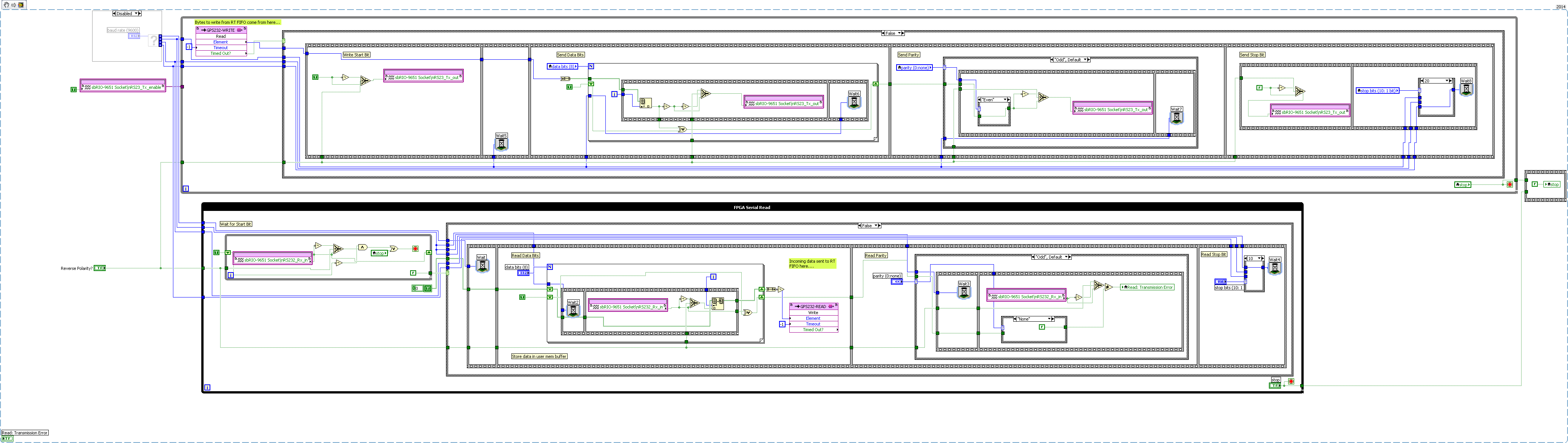

I can't find a way to reattach my compilable version of your VI to this thread, so I've embedded the code into this VI Snippet. You should be able to drag and drop this picture into a blank VI block diagram and it will embed the code (unless the website has pulled my encoded VI from the .png.)

National Instruments

To the pessimist, the glass is half empty; to the optimist, the glass is half full; to the engineer, the glass

04-22-2015 01:01 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Tanner, Spex,

I did many, many times, delete and replace the I/O nodes. I even opened a new VI and dragged the nodes from the Project and STILL got the compile error on the 'fresh' vi.

At this point, I am NOT using a custom CLIP - I am using the Devkit CLIP as-is because I need to get this project back on schedule. Although I will eventually have to create a custom CLIP when we install the SOM on our board.

Regards

Jack Hamilton

04-23-2015 09:28 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Jack,

Right now, we are seeing different behavior than you. You might have already tried this, but can you:

1. Create a brand new LabVIEW project and add the sbRIO-9651.

2. Use the sbRIO CLIP Generator to create a brand new Socketed CLIP that has the same properties as your current, custom CLIP.

3. Create a new LabVIEW FPGA that has an identical top loop as the one in question. Try not to copy/paste the previous project code. Also, leave out the calculation subVI as that could also potentially be corrupted.

4. Attempt to compile the newly-created VI.

Also, can you please ZIP your entire LabVIEW project with all of it's dependent files and attach it to this page? Please verify that you do not have any sensitive information, data, or IP as this is a public page.

- Tanner

National Instruments

04-23-2015 07:40 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Tanner,

Did what you asked. It compiled and ran fine. The zip is attached to my original post of this thread. (can't upload files on replies?)

Jack

05-15-2015 05:05 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Jack,

This looks like it may be a VI corruption. It's hard to say what might have caused this to occur without being able to reproducibly cause this corruption. Have you seen this come up again since replacing the I/O node?

Bryan

05-15-2015 06:17 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Bryan,

I've not recreated the conditions that lead to the problem. Which occured multiple times. I've been using the Devkit and the DevKit CLIP unchanged, as I've got to get the project moving forward.![]()

I will note that I did start with a cRIO project, to migrate code from the cRIO to the SOM sbRIO.

This can be the problem...as you CANNOT open a new cRIO project and 'import' a SOM as a target device....I can only import the SOM on a new sbRIO project. (I am not sure how I pulled in the sbRIO SOM on the existing cRIO project in the first place...)

I find this odd, from the user perspective, as I would be likely to convert cRIO code over to sbRIO...as projects go from prototype to brassboard. So I'd open my cRIO project, pull in the sbRIO target and start moving the FPGA and RT vi's over...

Does this help?...can you expand in why I cannot pull any cRIO into a sbRIO project? and vice versa?..![]()

Regards

Jack Hamilton

05-18-2015 01:00 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Jack,

There shouldn't be any issue adding a new target (sbRIO, SOM, or otherwise) to an existing project. I suspect your difficulty is a result of poor user experience design in the LabVIEW project.

To add a new target to an existing project, you have to right-click on the 'Project: [my project].lvproj' entry in the project tree view and select New>>Targets and Devices... From the resulting dialog box, you should be able to add any target to the project, and begin moving files and VI's between RT targets and FPGA targets. If you right-click any other item in the project and select New>>, then you will have limited target selections, such as if you right click on a CompactRIO RT target, and select New>>Targets and Devices..., then your resulting options will only be CompactRIO chassis, because the dialog box inherits from the item you originally right-clicked.

Please let me know if this does not match your experience.

Including screenshots of my LabVIEW project adding new targets, and a project with CompactRIO and Single-Board RIO.

National Instruments

To the pessimist, the glass is half empty; to the optimist, the glass is half full; to the engineer, the glass

- « Previous

- Next »