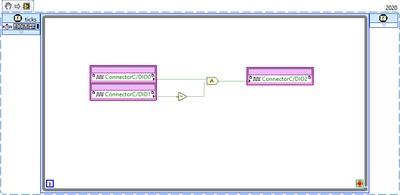

When creating a basic FPGA code like the one attached, even when running at a maximum of 400MHz and with zero synchronization registers, there is still a 2.5ns jitter observed during execution. If the code itself does not necessitate any clock input, is it feasible to configure the FPGA to operate independently from a clock, functioning solely as a simple logical "AND" element? In other words: is it possible to generate a potentially delayed signal on the output pin, however with minimal jitter compared to the input signal?