Hello,

I'm using sbRIO9651 to receive LVDS data from ADC output (LTC2174). But I can only find the Labview example for NI658x which is a serie of special hardware for LVDS receiving.

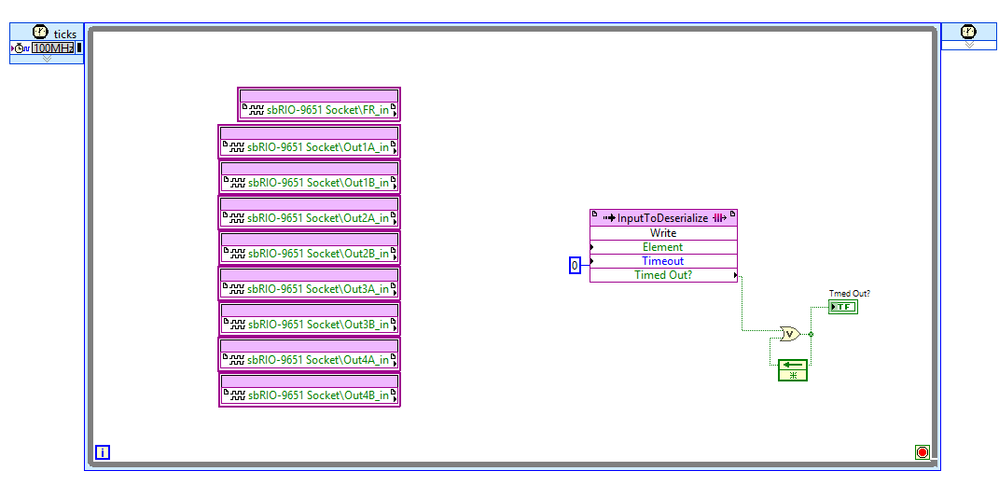

In my work, the ADC have 4 output channels and each channel has 2 lane (out1A out1B...out4A out4B). Each lane is connected to a DIO pin of FPGA (see picture). The data clock of ADC (DCO) is very fast (400MHz), so I can't use this clock for SCTL of LVDS data receiving. I was wondering that using a slower clock which is derived from DCO for LVDS receiving SCTL. E.g. 100MHz, but in this case, 7 bits will be outputed each lane in each iteration of SCTL.

How can I receive and save those LVDS output bits (e.g. in a array)? And then these bits data can be processed in later steps.