- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »

Regarding passing values between two targets

12-01-2014 11:29 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

BMac,

in reference to your comment "..If you decide you want to go with FPGA-to-FPGA communication for low latency reasons, let me know and I can share some example code for serial UART communication with packet decoding. ..."

could you provide me with the example codes please?

12-02-2014 03:15 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Could you provide a working example for serial UART for the FPGA-to-FPGA communication please.

12-02-2014 10:42 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You bet. I'm cleaning up some code and testing. Assuming things go well I should be able to share it tomorrow.

Regards,

Brian

12-08-2014 05:25 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Status update: This has taken longer than expected because of competing projects. But I am wrapping things up now on the serial interface code and expect to have it ready to share tomorrow. Thanks for your patience and sorry for the incorrect post on when it would be available.

12-09-2014 10:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

An updated version of the GPIC Reference Design application with support for the new AgileStack Power Converter Evaluation Kit is available below. To increase the reliability and reduce operating costs, the new AgileStack power converters are truly digital power converters that provide extensive built-in monitoring and diagnostic capability along with highly configurable fault detection, management, and recording. This combines with the extensive digital signal processing and advanced control capabilities of the NI General Purpose Inverter Controller, which provides a heterogeneous FPGA control platform with 58 embedded DSP cores and high level graphical programing tools with fully integrated model based design and power converter global optimization tools, including real-time power electronics simulation capabilities.

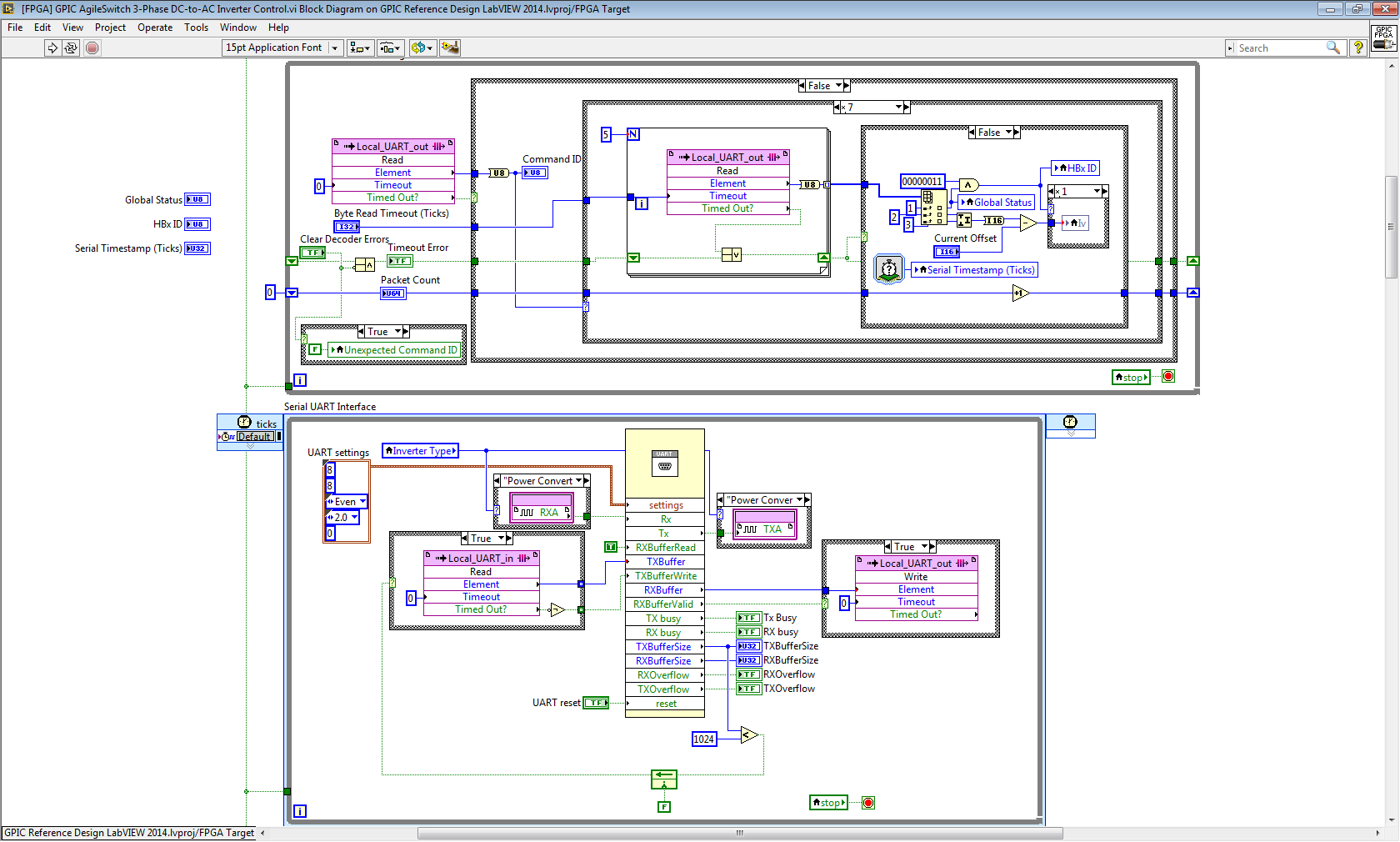

This example code includes the 5 Mbps serial UART interface to the AgileStack with FPGA based decoding of the serial packets containing the 3 phase currents, 3 half-bridge temperatures, and the DC link voltage. The GPIC analog inputs provide 3-phase grid and phase voltage sensing. The code includes the complete FPGA, RT, and Windows desktop user interface applications for the DC2AC converter, although automatic fault capture/logging is not currently implemented.

To extract, you must use 7-Zip or Winzip (not Windows built in ZIP archive utility) and you must unzip to a very short path such as "C:\PowerDev\" (not to your desktop):

ftp://ftp.ni.com/evaluation/powerdev/training/GPICReferenceDesign2014AgileStack.zip

A screenshot of the GPIC Serial UART Interface and Pack Decoder Logic is shown below, from "[FPGA] GPIC AgileSwitch 3-Phase DC-to-AC Inverter Control.vi".

See also the simple control and serial interface example under the FPGA UART folder, named "[FPGA] GPIC AgileStack Control.vi".

Notes:

- In all of the examples, FPGA-based fault capture will be moved to the real-time processor application (using the DMA data stream) to free up a significant amount of FPGA resources. In the AgileStack DC2AC converter application, the real-time processor based fault capture feature has not yet been implemented. (In the SKiiP3/Methode SmartPowerStack examples, the FPGA-based fault capture implementation remains unchanged.)

- An AgileStack example for DC2DC converter has not yet been implemented.

- You will need to first update the AgileStack firmware and then reboot it (unpower, repower) per instructions from AgileSwitch. This is located on the website at: www.agileswitch.com/download.page

01-21-2015 03:39 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Is there a simpler example for UART that I could work with, like a standard UART interface for baud rates of say 9600bps?

01-22-2015 08:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

If you are familiar with VHDL, there is a very simple fixed function IP core available from OpenCores. However, it does not have the same features and configurability.

http://opencores.org/project,uart

Here are application notes on how to integrate the VHDL into LabVIEW FPGA using the IP Integration Node.

Importing External IP Into LabVIEW FPGA

Using the IP Integration Node (FPGA Module)

http://zone.ni.com/reference/en-XX/help/371599K-01/lvfpgaconcepts/ipin_use/

Preparing IP for Use with the IP Integration Node (FPGA Module)

http://zone.ni.com/reference/en-XX/help/371599K-01/lvfpgaconcepts/ipin_prepare_ip/

- « Previous

-

- 1

- 2

- Next »