- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Scaling errors(?) when sampling an analog signal.

10-09-2009 03:06 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Setup:

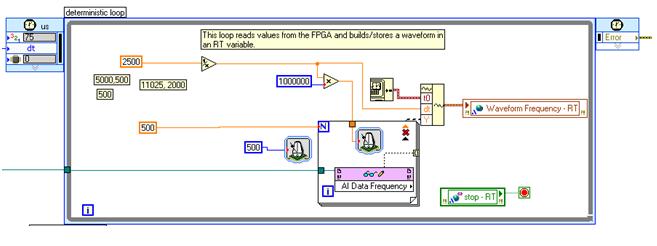

I am trying to sample an analog signal using a cRIO 9073 and the NI9205 Analog input module. I am not using the SCAN engine, I am using the FPGA tools. I am trying to detect a frequency of ~400Hz. I've got a loop on my FPGA that reads a value from the analog input with a loop timer of 100us (this should allow me to read at a rate of 10kS/s accurately). I have a loop on the cRIO that reads values obtained from the FPGA and creates a waveform. The loop uses a "S/s" value to determine the value of the loop time (dt of the waveform) and a "# of Samples"value to determie how many samples to take (N of the FOR LOOP). These values are placed in an array and when the loop in done the array is input to a build waveform (Y).

Problem:

I am currently sampling at 2500 S/s for 500 samples creating a 200ms sample time and I am detecting the ~400 Hz frequency. I would like to increase the frequency range I can observe and so I have increased my sample rate to 5000 S/. When I do this the ~400Hz signal is read as ~800-900 Hz (I can't say it is exactly 2x of the actual signal). I am not sure why this occurs. I have tried several S/s&# of Samples combinations to keep the same data acquisition time but have had no success.

Below is a screen capture of the cRIO loop obtaining the FPGA values and creating the waveform (in my project there are no broken paths). Any suggestions? Thanks in advance.

10-09-2009 04:48 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

5thGen wrote:Setup:

I am trying to sample an analog signal using a cRIO 9073 and the NI9205 Analog input module. I am not using the SCAN engine, I am using the FPGA tools. I am trying to detect a frequency of ~400Hz. I've got a loop on my FPGA that reads a value from the analog input with a loop timer of 100us (this should allow me to read at a rate of 10kS/s accurately). I have a loop on the cRIO that reads values obtained from the FPGA and creates a waveform. The loop uses a "S/s" value to determine the value of the loop time (dt of the waveform) and a "# of Samples"value to determie how many samples to take (N of the FOR LOOP). These values are placed in an array and when the loop in done the array is input to a build waveform (Y).

Problem:

I am currently sampling at 2500 S/s for 500 samples creating a 200ms sample time and I am detecting the ~400 Hz frequency. I would like to increase the frequency range I can observe and so I have increased my sample rate to 5000 S/. When I do this the ~400Hz signal is read as ~800-900 Hz (I can't say it is exactly 2x of the actual signal). I am not sure why this occurs. I have tried several S/s&# of Samples combinations to keep the same data acquisition time but have had no success.

Below is a screen capture of the cRIO loop obtaining the FPGA values and creating the waveform (in my project there are no broken paths). Any suggestions? Thanks in advance.

the above diagram is flawed due to the assumption that the for loop collecting data is acutally running at the assumed rate. the reading from the FPGA takes a finite amount of time, say 400 usec. the case that succeeds is greater than this value and the case that fails is less than this value invalidating the assumption of timing. this can be verified by timing how long the loop takes to execute.

The correct way to do this is to use a DMA transfer from FPGA using the FPGA to time the intersample delay and have the RT read all points out of the DMA FIFO then process.

10-12-2009 08:41 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Stu has pinpointed the solution exactly. I also strongly advise that you not use wait functions within your timed loop. You have already defined the timing for the loop with the dt parameter, so using the Wait for Next [ms] Multiple is rarely appropriate. If you want to wait for set times within your timed loop, right-click on the timed loop and select "add frame" so that you can explicitly define these within the framework of the timed loop.

Gerardo