- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Error -61496 during FPGA compile

04-14-2015 09:46 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I am getting this error -61496 after adding two digital lines for Tx and Rx for FPGA serial. I've tried several different configurations of the lines to make this error go away, but cannot.

I am certain it's the I/O lines, because when I remove the I/O line calls from my FPGA code - it compiles without error. I cannot find any information on this error.

What is odd is I am adding to existing FPGA code that has 4 I/O lines for I2S which compiles fine.

I've attached the CLIP folder zipped for review.

ADDED: ni_support.zip of the software configuration

04-14-2015 01:03 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Jack,

I went ahead and quickly create a new LabVIEW Project and added your SOM9651R1_13 CLIP to the project and compiled a blank bitfile. It looks like only Serial2 is enabled. I did not run into any errors during the compiliation, however.

I was attempting to reproduce what you are seeing but was unsucessful. If you do the same as me and create a new project, add the CLIP in question, and compile, do you still see an error?

I have not had a chance to look at the CLIP VHDL yet, but did you use the sbRIO CLIP Generator for the complete generation of the CLIP, or have you modified it since the initial creation?

Can you send a MAX Technical Report which lists your versions of NI software? This will help eliminate any incompatibilities. I am using LabVIEW 2014 SP1 and RIO 14.5.

- Tanner

National Instruments

04-14-2015 02:36 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Tanner,

Thanks for your quick response. It appears your suspicion was correct!. The software must be corrupted on that Development Computer - which I recently setup.....OR it is a Win8.1 (64-bit) Professional OS issue?!

I tried the _13 CLIP on my laptop (Win7 64-bit) and it compliles without error.

The error is so obscure that it first I thought it was related to FIFO's or the FPGA Serial Example Code which was in FPGA version 8 from the NI site.

I'll reinstall all the dev code again and report back.

Jack

04-14-2015 05:17 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Jack,

LabVIEW FPGA 2014 (and 2014 SP1) doesn't officially support Windows 8.1.

This gap in OS support is created because of the dependancy on the Xilinx Vivado compiler. LabVIEW FPGA 2014 and 2014 SP1 rely on Vivado 2013.4. Xilinx supported Windows 8 and 8.1 in Vivado 2014.1, which released in May 2014; too late to include in the LabVIEW FPGA 2014 distribution and test sufficiently.

I've seen a series of NI and Xilinx customers report strange/inconsistent compile behavior when running Vivado 2013.4 and/or LabVIEW FPGA 2014 on Windows 8. With that history, your errors don't surprise me, but it is frustrating how they manifest and appear to be tied to your code.

[Edit]: If you must use the Windows 8.1 Dev machine, you should consider trying to compile via the LabVIEW FPGA Compile Cloud service. All active LabVIEW FPGA SSP customers should have access to the compile cloud included in their SSP subscription (and the first year of subscription is included with initial software purchase.) When using the cloud, the Xilinx compile tools will be hosted on a compile machine with a supported OS, and while NI hasn't offically supported LabVIEW FPGA 2014 on Windows 8.1, I suspect the majority of bugs are on the compilation process. As an added benefit, the cloud compiles are farmed to Linux super computers, so they are noticably faster than most local compile options.

If you can't use the cloud compile service, you can also try to use the Windows 7 dev machine as a remote compile worker for the Windows 8.1 development tools.

Getting started with the LabVIEW FPGA Cloud Compile service

-spex

National Instruments

To the pessimist, the glass is half empty; to the optimist, the glass is half full; to the engineer, the glass

04-14-2015 07:06 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Spex,

Thanks. It saved my attempting a de-install then a full reinstall of LV Dev & FPGA...about a day!.

I'll subscribe to the Cloud Compile Server.

Regards

Jack Hamilton

04-16-2015 10:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Spex, Tannerite,

I still get this error after wiping my machine and installing Win7_64 bit OS and LV 14 SP1 over again. My other FPGA code compiles fine (I2S) but when I try to compile and updated version of the NI FPGA serial example with SOM FIFO's and Tx, Rx I/O from a new CLIP (My CLIP_13 attached).

It throws this error. In fact it throws it error if I write a VI with only the Tx, Rx line calls in a single loop.

I did download the Vivado 2013.4 tools and Xilinx 14.7 tools as my LV2014_SP1 update did not include these.

Any help appreciated.

Jack Hamilton

04-16-2015 10:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

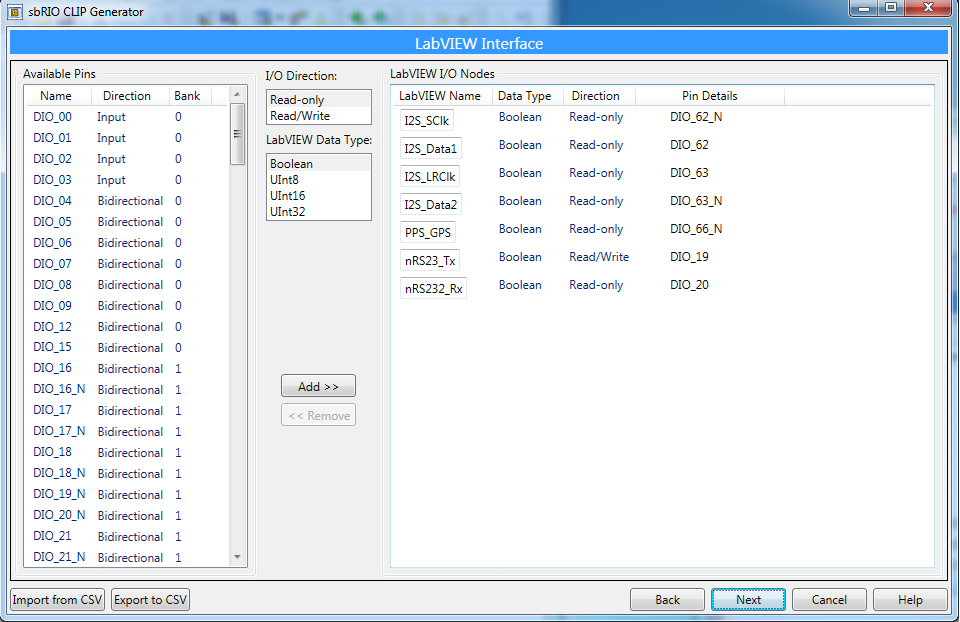

I wanted to post some details on how I've configured the CLIP for RS232, I wish to use the PMOD_1 inteface pins because they appear to be protected with transceivers so I don't hurt the SOM wiring 3.3 RS232 directly.

So I've configured Pins 19 and 20 for Rx and Tx. The unknown for me was it seems by default all NI SOM examples CLIP configure lines as 'bidirectional' in the pin configuration - even though a serial TX is an output only - but this seems to be configured on the "LabVIEW Interface" CLIP cfg page.

04-16-2015 10:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

(Sorry about two posts, but the forum posting has odd behavior when inserting a pic -all my text dissappears!)

On the "LabVIEW Interface" page, I assign Pins 19 as Tx "Read/Write" and Rx and "Read-only".

04-16-2015 10:57 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

QUESTION: Now when I update the revised CLIP to my SOM. I notice the SOM I/O list updates and shows three 'properties' for the Tx line as shown: Tx_in, Tx_out, Tx_enable.

Also when you drop the I/O calls on the diagram, the VI run>error reports you need the 'enable' function. Which I am guessing at the start of the VI and set to "TRUE".

04-16-2015 10:59 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Please note in my original top-level of this post I've ADDED the FPGA SOM Serial code. Which should allow you to add my CLIP and compile my code under the FPGA SOM.

I also get his error on another Win7 64 machine with this code/project/CLIP that have been a very reliable LabVIEW development computer.

Regards

Jack Hamilton